半導體封裝技術深度解析:晶片的「高訂服裝」有哪些門道?

當晶片製程逼近物理極限,封裝技術如何從幕後走向台前,成為推動AI、高效能運算時代的關鍵力量?一起來探索晶片從裸晶到成品的奇幻旅程。

嘿,大家最近好嗎?聊到科技,我們總會先想到那些酷炫的AI應用、功能強大的智慧型手機,或是運算速度飛快的電腦。但你有沒有想過,支撐這一切的核心——那片小小的晶片,是怎麼樣從一塊脆弱的矽晶圓,變成能夠穩定運作、抵禦外界干擾的強大心臟的?老實說,我以前也覺得這塊很神秘,直到一頭栽進去研究,才發現「半導體封裝」這門學問,簡直就是晶片的「時尚大秀」,充滿了各種令人驚嘆的工藝與巧思。

過去,大家都在追逐摩爾定律,比誰的製程更小、更精密。但當製程來到奈米等級,單純的微縮已經越來越難,成本也越來越高。這時候,封裝技術就從過去的配角,一躍成為鎂光燈下的主角。它不再只是單純的保護殼,而是肩負起提升晶片效能、降低功耗、縮小體積的關鍵任務。可以這麼說,沒有先進的封裝技術,再厲害的晶片設計也只是紙上談兵。

今天,就讓我們一起來揭開半導體封裝的神秘面紗,看看晶片是如何穿上它專屬的「高訂服裝」,從傳統走向未來。

傳統封裝:打下基礎的經典款

讓我們先從「傳統封裝」說起。這就像是晶片的「基本款」或「經典款」服裝,雖然不像現在的技術那麼花俏,卻是整個半導體產業發展的基石。在早期,晶片的功能相對單純,封裝最主要的目的就是保護脆弱的裸晶(Die),並透過金屬引腳(俗稱的「腳」)將晶片與外部的電路板(PCB)連接起來。

你可能聽過一些名字,像是DIP(雙列直插式封裝),就是早期電腦裡常見的那種長方形、兩排像蜈蚣腳一樣的晶片;還有SOP(小外形封裝)、QFP(四方平面構裝)等等。它們的共同點是,先將切割好的單一裸晶固定在一個基板上,然後透過「打線接合」(Wire Bonding)的方式,用極細的金線將晶片上的電路連接到封裝的引腳上。這個畫面,想像起來就像是給晶片進行一場極度精密的微創手術。

雖然這些傳統封裝技術成本低、技術成熟,但它們的缺點也相當明顯。隨著晶片功能越來越複雜,需要連接的I/O(輸入/輸出)數量暴增,那些又長又佔空間的引腳很快就不夠用了。更重要的是,從晶片到電路板的訊號路徑太長,就像開車繞遠路一樣,不僅速度變慢(訊號延遲),還更耗油(功耗增加)。對於追求輕薄、高速的現代電子產品來說,傳統封裝顯然已經力不從心。

先進封裝:異質整合的世代來臨

當傳統封裝遇到瓶頸,就輪到「先進封裝」登場了。這不僅僅是衣服款式的改變,更是一場從「平面」走向「立體」的思維革命。先進封裝的核心概念是「整合」,它不再滿足於一次只封裝一顆晶片,而是要想辦法在一個小小的封裝體內,塞進更多、功能更不同的晶片,也就是所謂的「異質整合」(Heterogeneous Integration)。

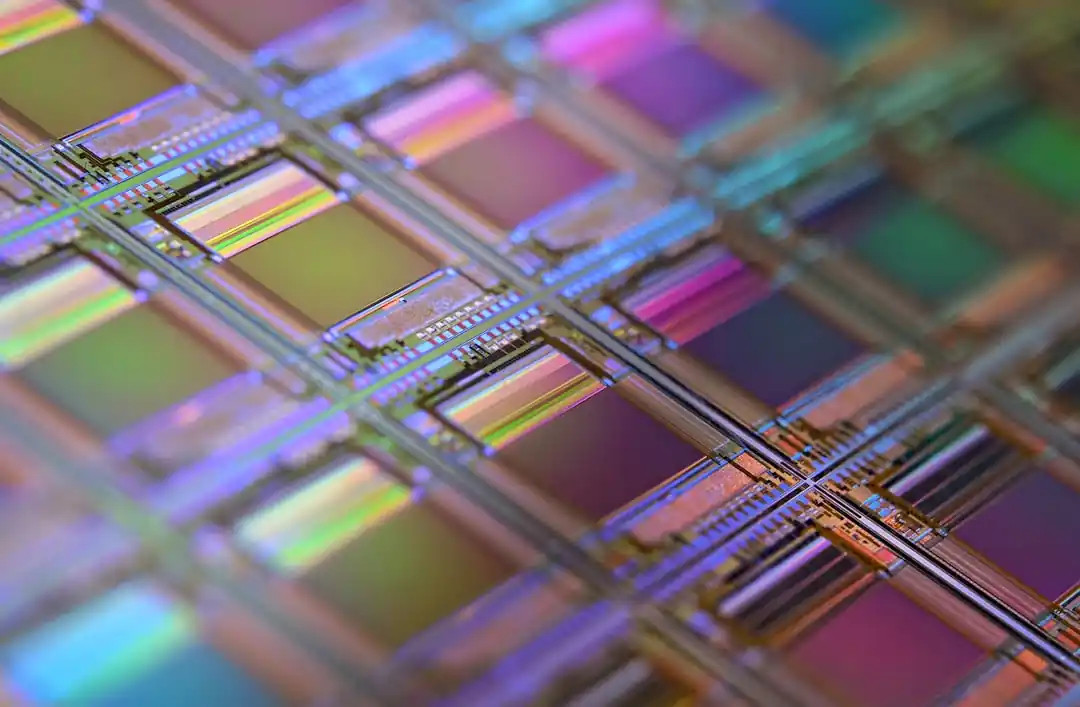

其中一個重要的技術突破是「覆晶」(Flip-Chip)。相較於傳統打線接合,覆晶技術直接在晶片上製作微小的焊錫凸塊(Bumps),然後像蓋印章一樣,將晶片翻轉過來,直接與基板連接。這大大縮短了電氣路徑,提升了效能和散熱能力。另一個關鍵則是「晶圓級封裝」(WLP),它改變了先切割再封裝的流程,直接在整片晶圓上完成大部分的封裝步驟,更有效率,也能實現更小的封裝尺寸。

而晶圓級封裝又衍生出「扇出型」(Fan-Out)技術,這更是讓先進封裝如虎添翼。簡單來說,它允許I/O連接點「扇出」到晶片原始面積之外,從而實現更高的I/O密度和更靈活的設計。這對於需要大量數據吞吐的AI和網通晶片來說,至關重要。

2.5D/3D封裝:蓋起晶片世界的摩天大樓

如果說先進封裝是從平房走向公寓,那2.5D和3D封裝技術,簡直就是在晶片世界裡蓋起了摩天大樓。這也是當前AI晶片領域最火熱的話題,尤其是台積電的CoWoS和SoIC技術。

2.5D封裝,以台積電的CoWoS(Chip-on-Wafer-on-Substrate)為代表,它引入了一個關鍵角色——矽中介層(Silicon Interposer)。你可以把它想像成一個超高精密度的轉接平台。CPU/GPU這些邏輯晶片和高頻寬記憶體(HBM)等不同的晶片,可以先並排放在這個矽中介層上,透過中介層內部極度微小的線路高速互通,然後再一起封裝到傳統的基板上。這樣做的好處是,既能讓不同晶片緊密合作,又能維持一定的設計彈性,是目前高效能運算晶片的主流方案。

而3D封裝,則更加極致。它不再需要中介層,而是直接將不同的晶片垂直堆疊起來。晶片與晶片之間,透過「矽穿孔」(TSV)技術直接打通,形成最短的垂直連接通道。台積電的SoIC(System-on-Integrated-Chips)就是這種技術的代表。這種「晶片疊晶片」的方式,可以實現最高的整合密度和最低的功耗,是未來行動裝置和AI晶片的終極目標之一。

應用與未來:封裝決定了科技的樣貌

從傳統到先進,從2D到3D,半導體封裝技術的演進,完全是跟著終端應用需求在走。簡單的消費性電子,或許用傳統封裝就已足夠;但對於追求極致效能的AI伺服器、需要兼顧功耗與體積的智慧型手機、以及分秒必爭的自駕車感測器,先進封裝就成了唯一的選擇。

特別是在AI時代,GPU的算力越來越強大,但如果沒有高頻寬記憶體(HBM)透過CoWoS這樣的先進封裝技術與之緊密配合,再強的算力也無法即時獲得足夠的數據,就像超級跑車沒有足夠的汽油一樣。可以說,先進封裝的能力,直接定義了AI技術發展的天花板。

展望未來,封裝技術的重要性只會越來越高。異質整合將成為常態,光學元件、感測器等更多不同功能的元件,都將被整合進同一個封裝中,創造出我們今天難以想像的應用。這趟從矽晶圓到終端產品的旅程,每一步都凝聚了無數工程師的智慧與汗水。下次當你拿起手機、讚嘆AI的強大時,不妨也想想背後這場精彩的晶片「時尚大秀」吧。

You might also like

薪水永遠不夠用?給台灣小資族的5個被動收入建立指南

月薪追不上物價,讓你感到焦慮嗎?這篇文章將分享5個在台灣真實可行的被動收入管道,從投資理財到發揮你的才華,一步步教你如何為自己加薪,擺脫月光族的宿命。

2026台灣曙光景點推薦:用第一道光,點亮你的新年序幕

新的一年,你想好要用什麼方式開始了嗎?對我來說,沒有什麼比親眼見證新年的第一道曙光,更能為生活注入滿滿的希望與能量了。一起來看看台灣有哪些地方,能讓你遇見最難忘的日出吧!

台南高鐵站一日遊:不進市區也能玩翻天!

誰說到台南一定要衝市區?高鐵站周邊其實隱藏著許多驚喜!從刺激的遊樂設施到靜謐的博物館,再到超好逛的Outlet,讓你一下車就能開啟精彩的一日遊。

台灣國內旅遊預算應如何分配?從交通、住宿到餐飲的省錢技巧

想在台灣來一場深度旅行,卻又擔心預算破表嗎?別擔心,這篇文章將帶你從交通、住宿、餐飲三大面向,全方位解析國內旅遊的省錢秘訣,讓你花小錢也能玩得盡興!

走進太陽的國度:西班牙安達盧西亞,一場不願醒來的夢

從熱情的佛朗明哥舞、摩爾人的古老宮殿,到懸崖邊的白色山城,這份安達盧西亞行程推薦,將帶你深入南西班牙的靈魂,感受陽光、美食與歷史交織的魅力。